Certainty in an Uncertain World: Building Functional Safety into FPGA Designs | Synopsys

Helicopters to Venus – Build and Debug Highly Reliable FPGA-based Designs | SynopsysПодробнее

Using Static Analysis For Functional SafetyПодробнее

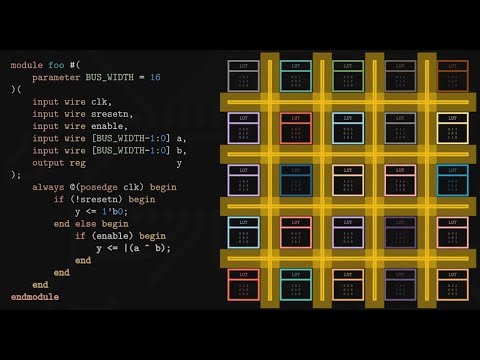

What's an FPGA?Подробнее

How and Where to “Design in” Functional Safety | SynopsysПодробнее

Summary | SynopsysПодробнее

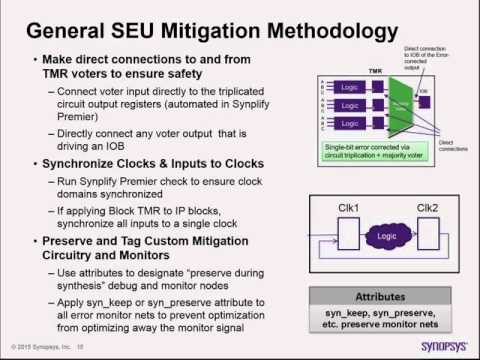

Safe-Guarding Logic, Registers, Clock Routing, IP, and I/O’s Using TMR | SynopsysПодробнее

ASIC and FPGA Workflow for ISO 26262 and IEC 61508Подробнее

Improve SEU immunity of FPGA based CPUПодробнее

Safe-Guarding FSM’s | SynopsysПодробнее

Test & Repair of SoCs for Functional Safety Applications | SynopsysПодробнее