Verilog HDL: 4-bit Adder using Data Flow Modelling

What is Multiplexer/Mux| #dataflow #multiplexer #mux #TestbenchSimulation #ModelSim #intellcityПодробнее

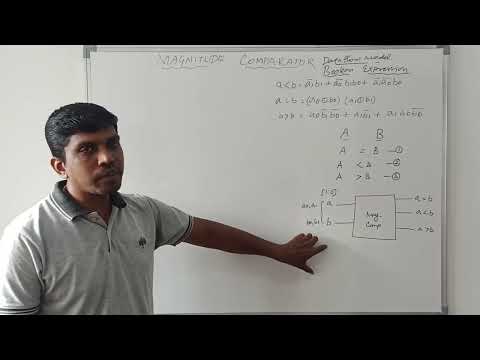

Magnitude Comparator Verilog HDL using Data Flow Model || S Vijay Murugan || Learn ThoughtПодробнее

Full Adder using Verilog Data Flow and Structural modeling.Подробнее

Design a 4 Bit Shift Register using Blocking Statement | Verilog HDL Program || Learn ThoughtПодробнее

How to Write 2 to 4 Decoder Verilog HDL Program? // Behavioral Model // S Vijay MuruganПодробнее

Experiment 1.b || 4-bit adder and subtractor || Verilog Code, Working Explanation || #verilogПодробнее

Dataflow Modeling - Verilog FundamentalsПодробнее

Test Bench Verilog Code for Full Adder - Behavioral // Learn Thought // S Vijay MuruganПодробнее

DSDV Complete Model Paper 1 Solutions | BEC302Подробнее

Design a Full Adder using Two Half Adder || Verilog HDL Program || S Vijay Murugan || Learn ThoughtПодробнее

How to Write Half Adder Program using Behavioral Modeling? || S Vijay Murugan || Learn ThoughtПодробнее

Binary to Gray Code Converter using Behavioral Modelling || Verilog HDL Code || Learn ThoughtПодробнее

How to write Half Subtractor Program Using Behavioral Modeling? || Learn Thought || S Vijay MuruganПодробнее

Full Adder using ternary Operator verilog code in dataflow modelПодробнее

Design a 1:4 De-multiplexer using Behavioral Model / VERILOG HDL / S VIJAY MURUGAN / LEARN THOUGHTПодробнее

To realize Half Adder circuit using Verilog data flow description.Подробнее

How to design and Write Verilog code for Carry LOOK Ahead Adder? || Learn Thought || S Vijay MuruganПодробнее

Design an 8X1 Multiplexer using Behavioral Modeling / Verilog HDL / Learn Thought / S Vijay MuruganПодробнее

How to Write Verilog Code for SR FF using Gate Level Modeling? || Learn Thought || S Vijay MuruganПодробнее

How to Write Verilog code for JK FF Using Case Statement? || Learn Thought || S VIJAY MURUGANПодробнее